## **Automated Sample Preparation of Low-k Dielectrics for FESEM**

R.R. Cerchiara\*, P.E. Fischione\*, J.J. Gronsky\*, J.M. Matesa\*, A.C. Robins\*, D.W. Smith\*, S.J. Rozeveld\*\*, C. Wood\*\*, E. Beach\*\*, and J. Waeterloos\*\*

\*E.A. Fischione Instruments, Inc., 9003 Corporate Circle, Export, PA 15632 USA

Rapid, efficient and automated sample preparation of microelectronic materials containing high-k dielectrics has been recently demonstrated.[1] A standard process cycle combines plasma cleaning (PC), argon ion beam etching (IBE), reactive ion etching (RIE), and ion beam sputter coating (IBSC) in a single vacuum chamber. An additional plasma cleaning step can be inserted after the RIE step, so that any residual contamination is removed prior to imaging or final sputter coating. This technique has now been extended to microelectronic materials that contain low-k dielectrics.

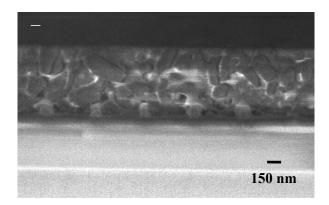

Because of their complex chemistry and low average atomic number, cross sections containing such layers often become damaged when mechanically sectioned or polished. The microstructure of an IMEC<sup>#</sup> Cu/porous-SiLK<sup>TM</sup> dielectric resin single damascene wafer after cleaving and plasma cleaning is shown in Figure 1. The Cu lines separated by the porous SiLK Y resin are barely visible below the rough fracture surface of the Si oxide and nitride layers. This sample was then processed according to the protocol summarized in Table 1. The total processing time was 28.5 minutes.

RIE of the high-k and low-k dielectrics was accomplished by forming a reactive gas plasma of Ar,  $CF_4$  and  $CHF_3$  which was directed perpendicular to the sample surface. Although chemically inert, the energetic Ar ions act to break Si-Si bonds, supplying Si to stabilize  $SiF_4$  vapor formation. Once the  $CF_4$  is ionized to  $CF_3$ , F is released ( $CF_4 + e - CF_3 + F + e - CF$

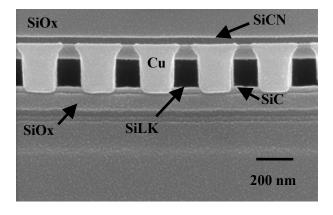

After FESEM imaging to assess the uncoated sample surface, a conductive coating of 6nm of Cr was added in a stand-alone sputter coater. This surface was re-imaged at 10kV and 100kX, Fig. 2. The action of Ar ions during IBE and later RIE resulted in the decoration of the Cu lines. The Ar/CF<sub>4</sub>/CHF<sub>3</sub> RIE resulted in delineation of the Si nitride and oxide, as well as of the porous SiLK resin. No significant amount of RIE residue was detected.

## References

[1] R.R. Cerchiara, P.E. Fischione, J.J. Gronsky, W.F. Hein, D.D. Martin, J.M. Matesa, A.C. Robins and D.W. Smith, "Recent Developments in Automated Sample Preparation for FESEM", Proceedings of the 29th International Symposium for Testing and Failure Analysis, Santa Clara, CA, Nov. 2-6, 2003, pp. 288 – 300.

[2] S.M. Rossnagel, Handbook of Plasma Processing, Noves Publications, New York, 1990.

# Sample courtesy of the Inter-University Microelectronics Center (IMEC), Belgium TM Trademark of The Dow Chemical Company

<sup>\*\*</sup>The Dow Chemical Company, Midland, MI 48667 USA

TABLE 1: Sample Preparation Protocol for IMEC Cu/P-SiLK<sup>TM</sup> Single Damascene Wafer

| Step | Process Gas                                | Time (min.) | Result                      |

|------|--------------------------------------------|-------------|-----------------------------|

| PC   | $Ar/25\%O_2$                               | 5           | Removal of Hydrocarbon      |

|      |                                            |             | Contamination               |

| IBE  | Ar                                         | 20          | Planarization               |

| RIE  | Ar/35%CF <sub>4</sub> /30%CHF <sub>3</sub> | 1.5         | Selective Etching of Low-k  |

| PC   | Ar/25%O <sub>2</sub>                       | 2           | Removal of Residue from RIE |

FIG 1: IMEC Cu/P-SiLK<sup>TM</sup> single damascene wafer after cleaving and plasma cleaning

FIG 1: Surface of cross section after PC + IBE + RIE +PC, followed by coating with 6 nm Cr