## **Etching Dynamics of Geometrically Confined Silicon Nanostructure**

Kunmo Koo<sup>1,†</sup>, Joon Ha Chang<sup>1,‡</sup>, Sanghyeon Ji<sup>1</sup>, Jacob Choe<sup>1</sup>, Seungmin Shin<sup>2</sup>, Geun-Taek Lee<sup>2</sup>, Tae-Hong Kim<sup>2</sup>, and Jong Min Yuk<sup>1,\*</sup>

- <sup>1.</sup> Department of Materials Science and Engineering, Korea Advanced Institute of Science and Technology, Daejeon, Republic of Korea.

- <sup>2.</sup> Advanced Core Equipment Engineering & Development P/J, Semiconductor R&D Center, Samsung Electronics, Hwaseong, Republic of Korea.

- †Current affiliation: Department of Materials Science and Engineering, Northwestern University, Evanston, IL, United States.

- ‡Current affiliation: Cathode Materials Research Group, Research Institute of Industrial Science and Technology (RIST), Incheon, Republic of Korea.

- \* Corresponding author: jongmin.yuk@kaist.ac.kr

Currently, semiconductor fabrication process is extremely shrunken in size and became intricated to form denser integrated circuits. As the size of the element within the transistor approaches to the width of several atoms, structure fabrication is facing unprecedent challenges. Among the multiple stages of device formation, chemical wet etching is a fast and low temperature process for removing unwanted material with high selectivity [1, 2]. However, the etching rate of material is significantly reduced compared to the bulk condition and stopped when it is surrounded by the dielectrics. This slow etching and unstripped debris became one of the major obstacles during the metallized gate and need to be conquered for the next generation processing node.

Liquid-phase transmission electron microscope (LPTEM) is a promising technique for observing materials in the liquid with a resolution of nanometers. Growth and assembly of the nanoparticles, dynamics of electrochemical reactions, catalytic reaction, and the structure of wet biological materials is previously revealed with various liquid cell configurations [3]. Aabdin *et al.*, have previously reported wet etching process of uncovered amorphous Si pillars using LPTEM, which has potential application to 3D semiconductor nanostructures [4]. Yet the actual semiconductor process nodes usually require the etching of nano-confined silicon patterns.

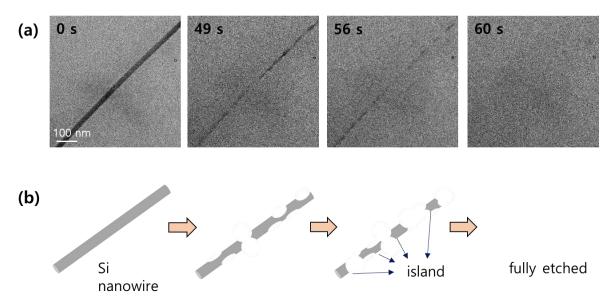

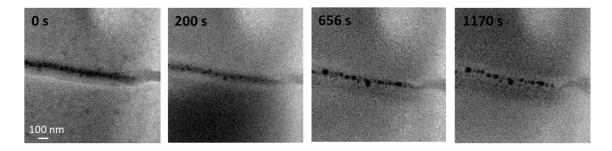

Herein, we have first demonstrated wet etching processes of exposed and confined crystalline Si using LPTEM. Crystalline Si nanowires with diameter of 20 nm were rinsed with 0.5 wt% of HF solution to remove native oxide on the surface. Then, they were drop casted on  $SiN_x$  e-chip with the heater element and assembled to the liquid TEM holder (Poseidon Select, Protochips, USA). For the confined nanowire, 50 nm of tetraethyl orthosilicate (TEOS) silicon oxide is deposited upon the Si nanowire with the gas injection system of focused ion beam (FIB) before assembling. Finally, 10 % (w/w) of TMAH solution is filled into the liquid cell with the syringe pump and heated up to 50 °C, which is the actual semiconductor process wet etch temperature. The time-series TEM image of etching process of uncovered Si nanowires are shown in **Figure 1**. The nanowire was etched in radial direction rather than the longitudinal direction, forming islands during the etch. However, when the nanowire is passivated with the TEOS oxide materials transport is significantly reduced and unetched Si nano-islands are trapped inside of the cavity (**Figure 2**).

**Figure 1.** (a) Real-time TEM images showing etching process of exposed Si nanowire. (b) schematic diagram of detailed explanation of (a).

Figure 2. Real-time TEM images showing etching process of confined Si nanowire

## References:

- [1] C. W. Pinion et al., Journal of Materials Chemistry C 4 (2016), p. 3890.

- [2] M. A. Gosa'lvez et al., Handbook of Silicon Based MEMS and Technologies: Second Edition (2015), p. 470.

- [3] F. M. Ross et al., Science **350** (2015), aaa9886.

- [4] Z. Aabdin et al., Nano Letters 17 (2017), p. 2953.